AI晶片技術專利系列五 - 輝達的GPU與台積電製程亦步亦趨

科技產業資訊室(iKnow) - 陳家駿、許正乾 發表於 2024年5月8日

圖、AI晶片技術專利系列五 - 輝達的GPU與台積電製程亦步亦趨

前面系列一到四談論的都是AI晶片的先進製程封裝技術與專利,本篇就來談論其上游IC設計。2023年的第二季開始,IC設計公司中的營收第一名是輝達,同時也是首度擊敗以往的第一、二名的高通(Qualcomm)與博通(Broadcom)。

其實自2023年初至2024年4月,輝達受惠於生成式AI的崛起,輝達的股價夯到不行,漲幅一度超過500%,甚至其高階晶片H100好幾度供不應求。也正因為AI已逐漸找到各種創新的應用場景,不論是汽車工業、AI伺服器、無人載具、影像顯示、生技醫藥、虛擬實境、軟體工程、智慧城市或金融科技等領域,都使得GPU的需求大增,迫使輝達的執行長黃仁勳三番兩次來台「綁樁」,鞏固其供應鏈能夠穩定接單、生產、交貨。

眾所周知,輝達專注在無晶圓廠的繪圖處理器GPU的設計,不同於本系列之前所提到的台積電、英特爾、三星電子與格羅方德等晶圓廠的製造技術。為了與前面系列的技術有相同的檢索基準,這次也同樣對AI系統-Lupix [1] 輸入與晶片堆疊有關的封裝技術特徵,「CoWoS可進一步拆分為CoW 和 WoS,CoW就是Chip-on-Wafer,將晶片堆疊,而WoS就是Wafer-on-Substrate,......,然後經由矽穿孔(Through-Silicon Via,TSV)技術來連結下方PCB基板(substrate),讓多顆晶片可封裝一起,以達到封裝體積小、功耗低、引腳少、成本低等效果。」

AI掃描出的結果,找到幾件相關的專利,而其中標題為「具一高功率晶片和一低功率晶片的低互連寄生現象的系統」(以下稱本專利)甚值關注,其台灣專利號為TWI515844B,而對應的美國專利號為US9728481B2 (System with a high power chip and a low power chip having low interconnect parasitics),分別於2016/01/01和2017/08/08獲證,目前本專利在機電技術領域中的專利價值之PR值(Percentile Rank)為96,也就是說,本專利的專利價值在機電領域中贏過96%的相關專利。

一般來說,在單一IC封裝中,為了降低所有晶片在印刷電路板(PCB)上所佔據的面積,通常會選擇將各晶片盡可能地在垂直方向做堆疊。這樣做還有另一個優點,那就是晶片與晶片之間的互連路徑是最短的,這將有助於縮短訊號傳輸的時間。然而,這樣的堆疊方式卻會衍生出散熱管理上的問題,例如高功率晶片(如CPU、GPU、NPU)堆疊在低功率晶片(如記憶體或I/O晶片)之上或下時,高功率晶片運作時所產生的高熱,會負面地影響鄰近的低功率晶片的效能。據此,本專利之發明就揭露一種在垂直方向上做晶片堆疊時,高、低功率晶片之間不僅仍保有最短的互連路徑,而且還能有效隔絕高功率晶片所散發出來的熱,更能降低IC中的寄生效應(parasitics)。

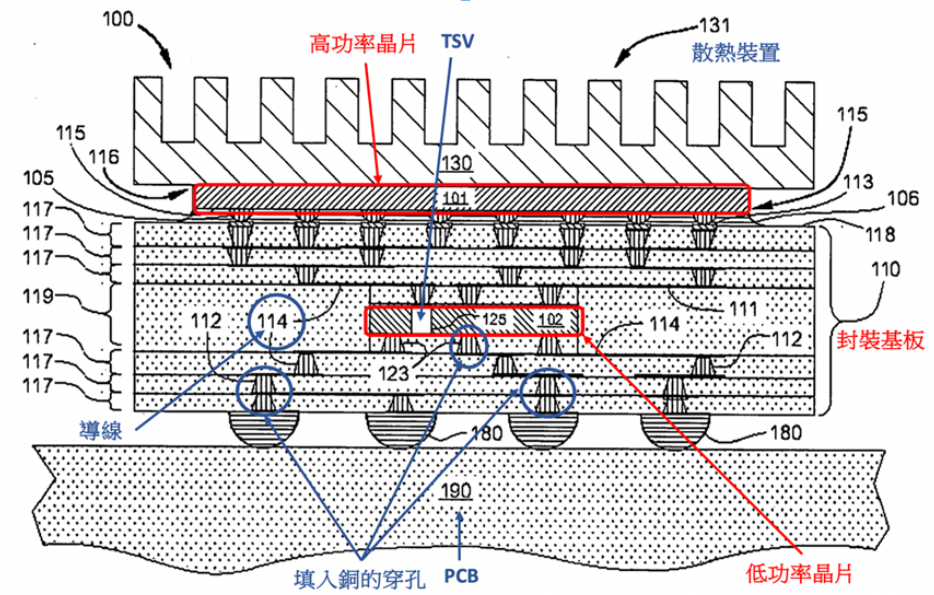

如圖1,係本專利所揭露的其中一種態樣的晶片堆疊結構示意圖。圖1中所示係在一PCB(190)上承載著一高功率晶片(101),並設置在一低功率晶片(102)的上方,其中低功率晶片(102)則被嵌入在封裝基板(110)內,高功率晶片(102)設置在封裝基板(110)外部。此外,依據本專利在獨立項中對高、低功率晶片的定義,高功率晶片(101)會產生至少10W的熱量,而低功率晶片(102)則產生少於5W的熱量。當高功率晶片(102)運作時所散發出的高熱,由於封裝基板(110)本身也有隔熱的作用,加上散熱裝置(131)可將高熱導引至IC的外部,所以如記憶體這樣的低功率晶片(102),就不易受到高熱而影響其運作效能。

此外,由於低功率晶片(102)又包含矽穿孔(125,TSV),透過矽穿孔(125)與其外部的多個已填入銅的穿孔(123)和導線(114),可將PCB(190)與高功率晶片(101)電性連接起來,因而在低功率晶片(102)和高功率晶片(101)之間,形成極短路徑長度的互連,進而造成快速的訊號傳遞、降低雜訊干擾與寄生現象等優點。

圖1、本專利的其中一種態樣的晶片堆疊結構示意圖

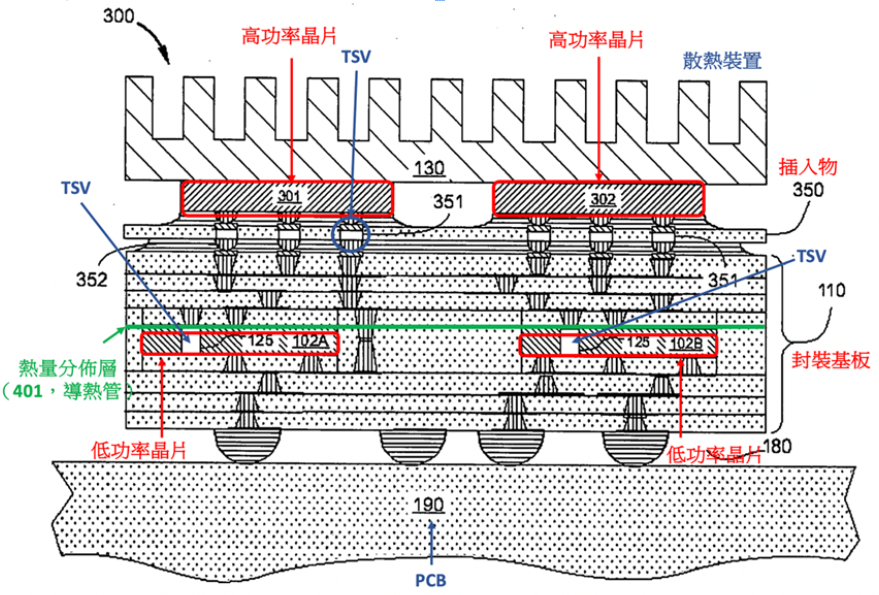

再參考圖2,是本專利所揭露的另一種態樣的晶片堆疊結構示意圖,也是本專利的代表圖。不難看出,圖2的晶片堆疊結構方式是基於圖1,只不過圖2的高功率晶片(301、302)是橫向並排的組態,而低功率晶片(102A、102B)分別被設置在高功率晶片(301、302)的下方,且被嵌入至封裝基板(110)中。

值得一提的是,根據專利說明書與圖2中的記載,「由一矽或玻璃基板形成的插入物(350),有著額外的IC晶片,如一或多個全球定位系統(GPS,Global Positioning System)晶片、射頻(RF,Radio Frequency)收發器晶片、Wi-Fi晶片。這些額外的IC晶片可藉由插入物(350)內設置的多層的金屬互連和穿孔與高、低功率晶片(301、302、102A、102B)電性連接。此外,插入物(350)提供高功率晶片(301、302)和低功率晶片(102A、102B)之間的額外隔熱,也因此而增加高功率晶片(301、302)之間的訊號傳遞。」

至於熱量分佈層(401)亦稱為「導熱管」(heat pipe),為具有高導熱性的材料,例如銅或鋁所組成,主要用來與低功率晶片(102)接觸,將低功率晶片(102A、102B)產生的熱量帶離,以降低運作期間低功率晶片(102)所帶來的過熱風險。

圖2、本專利所揭露的另一種態樣的晶片堆疊結構示意圖

整體而言,本專利是針對三維空間在垂直方向上的晶片堆疊之互連做保護,目的是在解決高功率晶片在大量運算時所散發的高熱,從而導致使晶片效能不彰與寄生現象。

記得輝達執行長黃仁勳在2023年11月,台積電創辦人張忠謀獲頒李國鼎獎之際,獲邀上台致詞,並說「沒有台積電就沒有輝達」。因此,為了探究輝達與台積電之間的關係到底有多緊密,利用本專利經過Lupix的語義分析比對,竟發現到一家「群成能源股份有限公司」(該公司的前身為「群成科技」,於2021年成為台灣光罩集團100%的關係企業),早在2010年12月22日就以美國優先權的方式,申請名為「三維系統級封裝疊層封裝結構」(Three-dimensional system-in-package package-on-package structure)之專利,並於2013年12月31日獲准美國專利,其專利號為US8619431B2(以下稱US 431專利)。

特別的是,就在2024年3月1日US 431專利已轉讓給台積電,而該US 431專利要解決的技術方案,正好就與輝達的本專利所記載的技術有一些關聯。由其中的專利交易脈絡可推測出,台積電不僅已經累積不少自家的3D IC製造方面的專利池,可能覺得專利佈局上仍有可再精進之處,所以正透過專利交易手段進行專利組合,這可能意味著台積電在未來進攻3D版的先進製程封裝的市場,有著強烈的企圖心,而現在正為了繼續保持「一個人的武林」,陸續暗中築起固若金湯的專利保護壁壘。

也許有人會問:「台積電不斷強化3D版的先進製程封裝專利,難道是為了輝達H100/H200/GB200 NVL72系列的產品嗎?」從輝達執行長黃仁勳自2023年下半年以來,頻頻造訪台積電的動作來看,的確令人玩味。(2344字;圖3)

作者資訊:

陳家駿律師 台灣資訊智慧財產權協會理事長

許正乾執行長 因子數據股份有限公司共同創辦人

註解:

[1] 因子數據自行開發的AI系統。

參考資料:

1. TWI515844B-具一高功率晶片和一低功率晶片的低互連寄生現象的系統. Google Patents,2011。

2. US9728481B2-System with a high power chip and a low power chip having low interconnect parasitics. Google Patents, 2011.

3. US8619431B2-Three-dimensional system-in-package package-on-package structure. Google Patents, 2010.

4. 中華民國專利資訊檢索系統https://twpat1.tipo.gov.tw/twpatc/twpatkm?000B15220007010100000000000100A00000003E000000000^_M。

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|