AI晶片技術專利系列三-三星電子的I-Cube蓄勢待發

科技產業資訊室(iKnow) - 陳家駿、許正乾 發表於 2024年5月3日

圖、AI晶片技術專利系列三-星電子的I-Cube蓄勢待發

三星電子於2024年3月初,發布新聞稿稱「將第二代3奈米製程的晶片改名為2奈米製造」,遭國內外許多媒體酸是為了想超越台積電而企圖魚目混珠,令人困惑且誤導大眾。姑不論三星電子是否真正具有2奈米的製造與量產能力,此舉反而凸顯來自台積電的競爭壓力,讓三星電子念茲在茲擬奮力一搏。繼半導體系列AI晶片技術專利系列2、3從技術與專利的視角,分析台積電CoWoS與英特爾EMIB的技術後,本篇再來看看三星電子在2.5D封裝技術面貌為何。

三星電子與台積電、英特爾一樣,都想極力發展出屬於自己的2.5D與3D封裝技術,根據三星電子的官網,目前最新的2.5D封裝技術為I-Cube (Interposer Cube),而3D封裝技術則為X-Cube (eXtended Cube)。由於本系列的前兩篇都是針對2.5D封裝技術做介紹,加上2.5D封裝又是目前市場的主流,所以本篇也以2.5D封裝技術來探討三星電子。

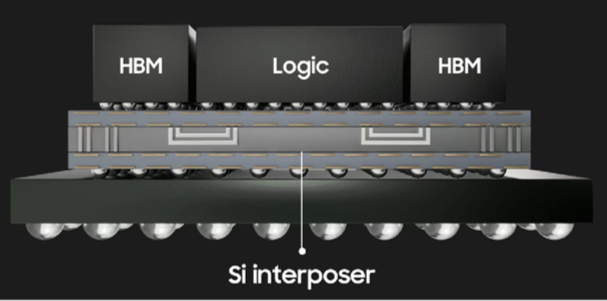

2.5D I-Cube分為I-CubeS與I-CubeE。如圖1-(a)所示,是三星電子的I-CubeS的半導體結構,而圖1-(b)所示則為I-CubeE的半導體結構。I-CubeS主要強調,即便在大型的中介層(interposer)上,搭載許多邏輯晶粒(die)與高頻寬記憶體(HBM),不僅有著令人驚嘆的頻寬,而且還有出色的翹曲控制(warpage control),以及超低訊號損失與高密度記憶體相結合,同時又有良好的熱效率控制(thermal efficiency control)。

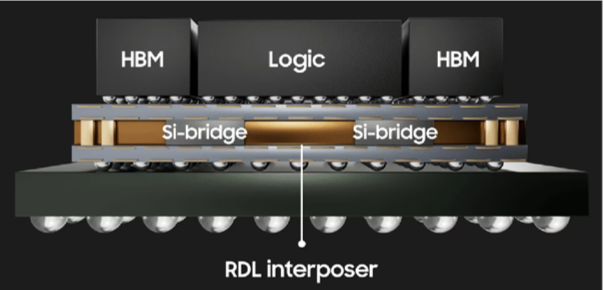

至於I-CubeE,主要採用矽嵌入結構,透過精細圖案化實現矽橋(silicon bridge),和FOPLP(Fan-Out Panel Level Package,扇出型面板級封裝),實現了無矽穿孔(TSV)和大尺寸的RDL(Redistribution Layer,重佈線層)中介層結構,不僅具成本效益,而且有優異的翹曲控制與功率完整性(power integrity)。

圖一、三星電子的I-CubeS的半導體結構

圖二、三星電子的I-CubeE的半導體結構

乍看之下,三星電子似乎是結合了台積電的CoWoS、與英特爾的EMIB的2.5D封裝技術。然而,通常矽中介層需要增加面積,以容納更多邏輯晶粒及HBM,而I-Cube的矽中介層比紙張更薄,僅大約100微米,這樣的中介層,是為了承載更多的邏輯晶粒與HBM,才必須使用大面積的中介層,但這樣的風險,就是在微觀尺度下容易產生彎曲或翹曲,造成負面影響。為此,三星透過改變材料與其厚度,研發出可避免中介層翹曲和熱膨脹的技術,以實現I-Cube的商業化。此外,這樣的半導體結構,還可防止運算時所產生的高熱積聚。

根據上述關於I-Cube的技術特徵,根據AI系統Lupix [1] 針對近10年的專利數據,掃描出與三星電子的I-Cube相關且符合當今具市場價值的已獲證專利。在眾多相關專利中,其中一項重要專利標題為「半導體封裝以及中介層」(以下稱本專利),其台灣專利號為TWI661522B,而對應的美國專利號為US10510647B2(Semiconductor Package,半導體封裝),分別於2019/06/01和2019/12/17獲證。AI系統Lupix根據當下的技術演化趨勢去做計算,推斷出本專利在機電技術領域中的專利價值之PR值(Percentile Rank)為94,也就是說,其專利價值高過94%的機電技術相關領域中的專利文獻。

如圖2所示,本專利中揭露一種半導體封裝結構之示意圖。根據其專利保護範圍來看,主要是透過中介層(110)內以金屬材料製成的複數配線層(wiring layer, 112)進行重佈線(redistribution),進而電性連接至GPU(131)與HBM(132、133)等晶片的連接墊(131P、132P、133P),藉此縮短訊號傳輸的距離,而這樣的功能就類似矽橋。

至於包封體(140)可保護GPU(131)與HBM(132、133)等晶片,保護層(150)可保護中介層(110)不受外部物理衝擊或化學衝擊,凸塊下金屬(underbump metallurgy,UBM)接墊(160P)不是簡單的圓形形狀,而是在平面中具有突出部分的齒輪形狀,以增大凸塊下金屬接墊(160P)與電性連接結構(170)之間的接觸面積,從而具有錨定效果且可分散應力(stress),進而提高電性連接結構(170)的可靠性。

圖三、三星電子的半導體封裝結構之示意圖

根據本專利的半導體封裝結構,可以解決封裝過程中可能會出現的翹曲,以及底部填充樹脂的可填充性劣化,更可以避免由於中介層的熱膨脹係數,與GPU、HBM等晶片在安裝過程中的材料不匹配所可能出現的裂縫問題。此外,透過本專利的中介層,還可有效地增大面積且降低成本。

針對台積電、英特爾與三星電子的2.5D版的先進封裝技術之發展,可歸納出幾個小結如下:

- 台積電的CoWoS,使中介層內的金屬線可電性連接多個晶粒的微凸塊(micro bump),以達到傳輸各晶片間的電子訊號,然後經由矽穿孔來連結下方PCB,讓多顆晶片可封裝一起。

- 英特爾的EMIB,不需要矽穿孔與中介層,僅透過矽橋即可電性連結不同的晶片並封裝在一起。

- 三星電子的I-Cube,將多個晶片插入中介層,然後透過中介層內的重佈線讓多個晶片進行訊號傳遞;此外,由於中介層的面積變大,使得可承載的晶片更多,也避免掉中介層可能發生的翹曲。

整體而言,三星電子的I-Cube與台積電的CoWoS、英特爾的EMIB一樣,都具備低成本、低功耗、低延遲、高頻寬、最佳化空間使用等優點,三者都有其應用場景,客戶可依照產品的不同需求可做選擇。然而,從過去市場上的聲量來看,台積電的CoWoS在AI和高效能計算(HPC)等領域上,可能更受市場歡迎。(1804字;圖3)

作者資訊:

陳家駿律師 台灣資訊智慧財產權協會理事長

許正乾執行長 因子數據股份有限公司共同創辦人

註解:

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|