小晶片處理器的創新挑戰在互連標準UCIe

科技產業資訊室 (iKnow) - Kyle 發表於 2022年4月26日

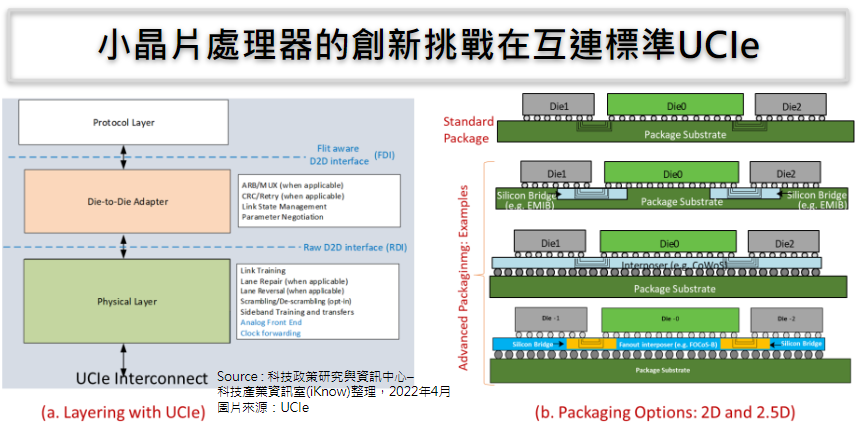

圖、小晶片處理器的創新挑戰在互連標準UCIe

超微、英特爾和輝達等許多世界上最大的晶片廠商都在投資小晶片,但是異質處理器並非沒有缺陷。

根據麻省理工科技評論,半導體產業已經承認製程節點大小將很快面臨停止縮小的窘境,也就是說,摩爾定律即將終結。有效迴避此節點大小限制的一種有前途的方法是晶片級異質整合。這意味著在一個封裝中連接多個專屬的、更小的半導體元件,以創建系統級封裝(SiP),而不是單晶片系統(SoC)。通過將晶片的功能拆分為稱為小晶片的更小設備,半導體製造商可以實現比單晶片更高的產量。

近年來,隨著基於小晶片的處理器(例如:超微的Zen 2)愈來愈受歡迎,產業研究和開發的重點是提高異質架構中的晶片間互連能力。

異質小晶片架構除了可以改善良率外,還允許製造商通過在單個封裝中組合不同類型的核心來創建優化的處理器。例如:異質行動處理器可以在單獨的小晶片上同時具有高性能、高功耗的核心,以及低性能、低功耗的核心。其可透過作業系統可以決定不同程式使用不同核心,以達到優化整體功率和性能的目的。

即便如此,基於小晶片的設計也有其自身的技術挑戰。基本上,SiP小晶片架構的主要障礙之一是建構具有成本效益、高性能和節能的die-to-die互連(Interconnect)。

與其他系統一樣,可用並行和串聯的物理層晶片到晶片互連,來達成廠商想要的晶片優勢。通常,現今存在三種類型的SiP幾何形狀:2D、2.5D和3D。

從歷史上看,基於小晶片架構和SoC架構通常使用2D封裝幾何形狀。對於這樣的幾何結構,兩個小晶片可能相距較遠,將SerDes PHY與時脈、數據串聯在一起,雖然不會產生傳播延遲,但卻會消耗更多功率。

為解決這個問題,半導體設計公司已經開始研究使用平行互連和中介層的2.5D和3D小晶片幾何結構。因為中介層允許小晶片堆疊,並大大減少數據和時脈訊號需要在小晶片之間傳輸的距離。至於平行互連,可以實現低很多的延遲傳輸,因為不再有與SerDes系統中的序列化、反序列化、編碼和解碼相關問題。

總之,隨著高性能運算和機器學習的興起,異質處理器必須處理的工作負載急劇增加。因此, Universal Chiplet Interconnect Express(UCIe)的新協議標準,可幫助整個半導體產業建立一個開放的小晶片生態系統。UCIe 是一種分層協議,它指定了物理層、die-to-die Adapter層和協定層,它允許2D和2.5D幾何形狀用於封裝。

也就是說,UCIe力求成為整個半導體產業使用的節能和成本效益標準,並可能在未來的異質架構中發揮關鍵作用。(936字)

參考資料:

Innovative Interconnects: The Future of Chiplet-based Processors? All About Circuits, 2022/4/18.

相關文章:

1. AMD全面採用chiplet小晶片技術而獲得了技術優勢

2. 台積電等成立UCIe標準聯盟,利用小晶片建構客製化SoC

3. 小晶片架構超級電腦的時代已經到來

4. 輝達CEO:加入英特爾成為代工夥伴、支持使用小晶片

5. 博通聯手台積電強化CoWoS平台 運用3D堆疊提高運算力

6. Arm為物聯網開發PlasticARM一種可彎曲微處理器

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|