邁入3奈米,EUV與相關周邊設備也須跟上晶片製造商腳步才是關鍵

科技產業資訊室 (iKnow) - Gloria 發表於 2020年11月30日

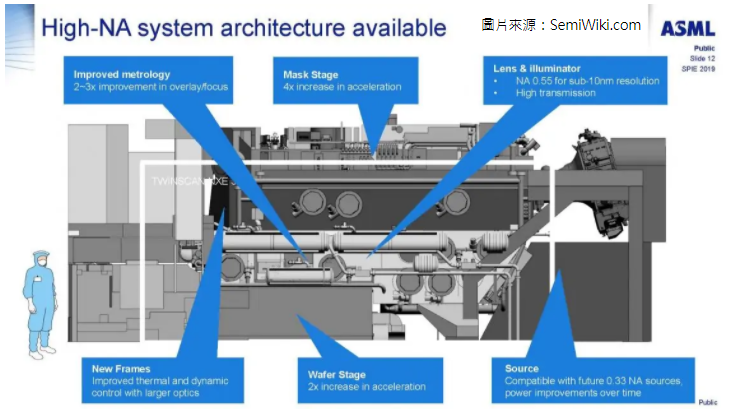

圖、High-NA EUV藍圖

2021年,ASML將提供為EUV掃描儀進行升級版,並且在藍圖中添加了另一個系統。ASML為下一代EUV掃描儀取了一個名稱high-NA EUV。根據ASML表示其新的光阻劑和光罩仍正在研發中。為了搶奪EUV市場,現今一些半導體設備供應商也正在開發新EUV相關設備。

EUV在5nm晶片的線路圖案(Pattern)技術下,使用單一圖案化方法,即可透過光罩將線路圖印在晶圓上。但是到了3nm製程之時,同一種方法不再適用,因此晶片廠商有兩種選擇。

第一個選擇是透過EUV雙重圖案化。第二個選擇,則是等待ASML開發出high-NA EUV系統,讓製程變得更為簡單化。可是high-NA系統不僅複雜又昂貴,而且剛剛推出時還存在一些風險.這表示著一旦ASML研發時程不順利,很可能拖延3 nm甚至更高製程的晶片推出時程。更重要得是,high-NA EUV系統必須等到2024年才能夠幫助3nm,這對於三星與台積電想搶在2022年採用3nm製程是一大障礙。

因此,晶片製造商別無選擇,只能採用EUV雙重圖案化的方式,讓晶片分為透過兩次光罩,然後將其印在晶圓上。這也是為什麼同一時間ASML也在研發EUV多重圖案化的方案。

基本上,EUV雙重圖案化需要在晶圓中執行更多製程步驟,這會影響到掃描儀的吞吐量。因此,晶片製造商需要更快速的EUV系統。目前ASML在其藍圖中增加了兩台多的0.33 NA EUV掃描儀。這是現今EUV掃描儀的升級版。第一個系統稱為NXE:3600D,吞吐量為160 wph。該工具計劃於2021年中推出。下一個工具的吞吐量為220 wph,計劃於2023年推出。

但是長期來說,3nm以及更先進製程仍需要high-NA EUV,以恢復到更簡單化的單一圖案模式方法。這不僅可以降低成本還能夠強化生產效率。目前ASML第一個high-NA EUV,稱為EXE:5000,吞吐量可達185 wph,計劃於2022年推出。至於更快版本的EXE:5200是預計於2024年推出。

根據投資銀行KeyBanc預估,現今一台的EUV掃描儀的成本為1.534億美元,可是一台high-NA EUV掃描儀的成本卻高達約3.186億美元。更重要的是,除了EUV之外,光阻劑、蝕刻,以及進入線路圖案之前的塗布顯影設備(Coater Developer)都很重要,因此未來3nm與更先進製程之戰,還有得瞧!(731字)

參考資料:

EUV Challenges And Unknowns At 3nm and Below. Semiconductor Engineering,2020/11/19

相關文章:

1. 台積電3奈米南科新廠上樑 在南科已投資2.1兆

2. 三星擴大投資1160億美元 目標於2022年超越台積電

3. 5奈米及3奈米戰爭=台積電與三星對壘

4. EUV成為ASML金雞母、台積電與三星代工競爭趨白熱化

5. 摩爾定律大突破、EUV助1.5奈米於2030年開出

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|