應用材料在晶片佈線大突破 邏輯晶片微縮至3奈米

科技產業資訊室 (iKnow) - May 發表於 2021年6月18日

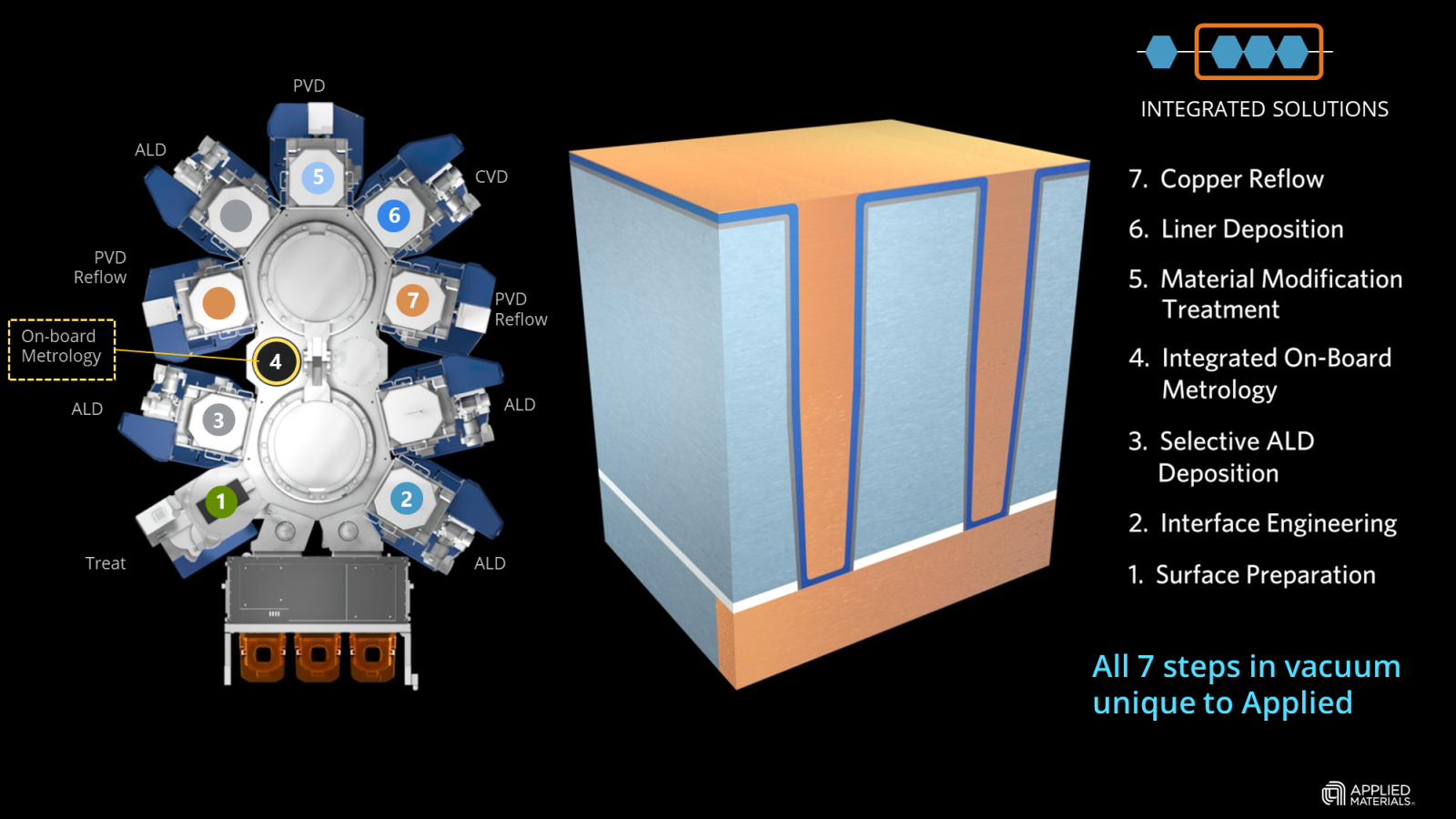

圖、應用材料EnduraCopper Barrier Seed IMS新材料工程解決方案

資料來源:Applied Materials,2021/6

美商應用材料(Applied Materials)是台積電供應鏈成員之一,宣布在晶片佈線技術大突破,促使邏輯晶片微縮到3奈米及更小尺寸。這也有助於台積電在3奈米製程開發。

應用材料(Applied Materials)公司於2021年6月16日公布一種全新的EnduraCopper Barrier Seed IMS銅阻障層晶種整合性材料解決方案,可在高真空環境下將七種不同製程技術整合在同一套系統中,而且該高級邏輯晶片佈線的新方法可擴展先進邏輯晶片微縮到 3 奈米節點及更小尺寸。

- 在晶片佈線方面的突破使邏輯擴展到 3 納米及以上

- 在真空下將七種不同製程技術整合到一個系統中,將互連電阻減半

- 新材料工程方法可提高晶片性能並降低功耗

- 最新系統體現了應用材料公司成為客戶 PPACt 支持公司的戰略

雖然尺寸減小有利於電晶體(transistor)性能,但互連佈線中的情況恰恰相反:較小的佈線具有更大的電阻,這會降低性能並增加功耗。如果沒有材料工程突破,從 7奈米節點縮到 3奈米節點,互連通孔電阻將增加 10 倍,從而抵消電晶體縮放的好處。

應材公司表示已開發出一種名為 Endura ® Copper Barrier Seed IMS™的新材料工程解決方案。它是一種整合材料解決方案,在高真空下將七種不同的製程技術結合到一個系統中:ALD、PVD、CVD、銅回流、表面處理、界面工程和計量。

這種組合用選擇性 ALD 取代了共形 ALD,消除了通孔界面處的高電阻勢壘。該解決方案還包括銅回流技術,可在狹窄的特徵中實現無空隙間隙填充。通孔接觸界面的電阻降低高達 50%,提高了晶片性能和功耗,並使邏輯縮放能夠持續到 3nm 及以上。

應用材料公司表示:「一顆智慧型手機晶片內含數百億個銅導線,佈線已用掉晶片三分之一的功率。在真空中整合多種製程技術,讓我們能夠重製材料和結構,讓消費者擁有功能更強大的裝置及更長的電池使用時間。這項獨特的整合解決方案是專為協助客戶加快發展效能、功率和面積成本的技術藍圖。」(603字;圖1)

Youtube視頻:Applied’s Unique Integrated Materials Solution Lowers Interconnect Resistance

參考資料:

APPLIED MATERIALS BREAKTHROUGH IN CHIP WIRING ENABLES LOGIC SCALING TO 3NM AND BEYOND. Applied Materials, 2021/6/16.

相關文章:

1. 應用材料正利用AI與大數據改變半導體設備產業

2. 賣方市場!半導體設備供應趕不上市場需求

3. 2021年3奈米製程開發加劇晶圓代工投資競賽

4. 台積電3奈米南科新廠上樑 在南科已投資2.1兆

5. 邁入3奈米,EUV與相關周邊設備也須跟上晶片製造商腳步才是關鍵

6. 台積電2奈米將採用哪種技術?

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|