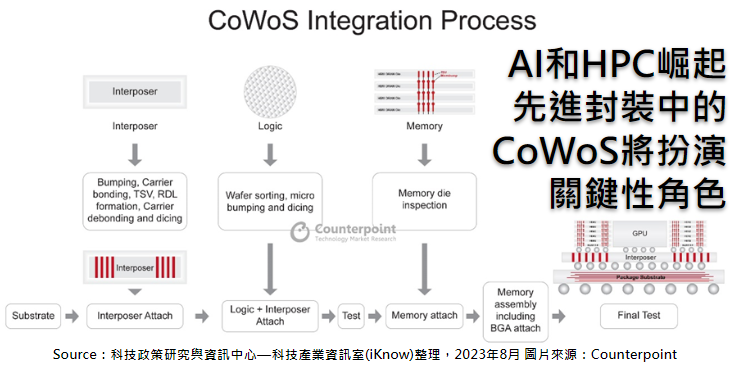

AI和HPC崛起,先進封裝中的CoWoS將扮演關鍵性角色

科技產業資訊室 - 茋郁 發表於 2023年8月2日

圖、AI和HPC崛起,先進封裝中的CoWoS將扮演關鍵性角色

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|