MIT團隊研發最大的碳奈米管微處理器,在5年內問世

科技產業資訊室 (iKnow) - May 發表於 2019年9月2日

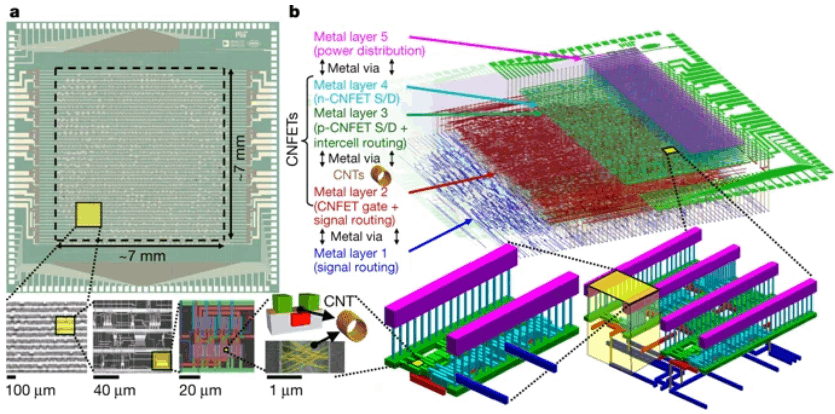

圖、MIT團隊研發最大的碳奈米管微處理器(RV16X-NANO)

圖片來源:Nature

麻省理工學院(MIT)研究團隊利用碳奈米管電晶體(Carbon Nanotube Transistors;CNFET)製造出一種新型微處理器,具有矽 10 倍的能源效率和更快的運行速度,已成為下一代電腦的主要目標。並且,他們採用了與傳統矽晶片的製程相同的生產方法,這給下一代電腦發展帶來了關鍵性突破,這種微處理器被廣泛認為是比傳統矽同類產品更快,更環保的替代品。預計這種完全由碳奈米管制成的CNFET晶片,可能在五年內上市。

一直以來,矽電晶體以 0 與 1 計算轉換的關鍵性微處理器元件,已經在電腦行業中存在了幾十年。預測未來有一天矽電晶體將受制物理極限而無法再縮小而告終。

該款碳奈米管微處理器的論文,發表在Nature 雜誌上,提供了 70 多頁的詳細製造方法,同時展示了一款具有超過 14,000 個CNFET的16位元微處理器,可執行與商用微處理器相同的任務。該16位元微處理器(RV16X-NANO)採用RISC-V 開源晶片架構,是具有一組微處理器可以執行的指令。該研究者Max M. Shulaker宣稱是由新興奈米技術製成的最先進的晶片,有望實現高性能和節能計算。

碳奈米管微處理器的3 大挑戰

Shulaker認為這款16位元微處理器,須解決生產碳奈米管微處理器的3 大挑戰:材料缺陷、製造缺陷和功能問題。

Shulaker說:由於,一小部分碳奈米管是金屬性的,這將減緩或阻止電晶體的開關。為解決這些問題,一個先進的電路可能需要純度約99.999999%的碳奈米管。因此,研究人員提出了一種名為 DREAM (designing resiliency against metallic CNTs,設計抗金屬性的碳奈米管)的技術,這個方法可以讓碳奈米管的金屬性不會干擾到計算。必須在過程中,將嚴格的純度要求降低了約 4 個數量級,即縮小了 10,000 倍,這意味著他們只需要純度達到 99.99% 左右的碳奈米管,而這是目前可以製備出來的。

設計電路通常需要一個由連接到電晶體上的不同邏輯門組成的庫,這些邏輯門可以組合在一起,就像字母組合在一起拼出單詞一樣來創建加法器和乘法器。研究人員發現,金屬性的碳奈米管對這些門的不同組合的影響是不同的。例如,A 門中的一個金屬性碳奈米管可能會破壞 A 和 B 之間的連接,但 B 門中的幾個金屬性碳奈米管可能不會影響 A 和 B 之間的任何連接。

於是,晶片設計時許多方法在電路上使用代碼。研究人員進行了模擬,以探索如何使所有不同門的組合都是穩定可靠的,且對於所有金屬性的碳奈米管都是相反的。然後,他們定制了一個晶片設計程式,自動地尋找最不受金屬性碳奈米管影響的組合。在設計新晶片時,程式只利用穩定可靠的組合,同時忽略了那些不穩定的組合方式。

找到製程過程去角質的關鍵方法

CNFET製造的第一步,就是將碳奈米管在溶液中沉積到具有預先設計好電晶體結構的晶圓上。然而,這過程中有些碳奈米管會隨機粘在一起,形成像義大利麵串成一大束小球一樣,在晶片上形成了大顆粒污染物。

為了清除污染物,研究人員發明了RINSE 技術(removal of incubated nanotubes through selective exfoliation,通過選擇性去角質的方法去除培養中的奈米管)。他們用一種促進碳奈米管粘合的試劑對晶圓片進行預處理。然後,在晶圓表面塗上某種聚合物,並浸入一種特殊的溶劑中。這樣可以將聚合物沖走,而且聚合物只能帶走大的碳束,單個碳奈米管仍會粘附在晶片上。與其他類似的方法相比,該技術可使晶片上的顆粒密度降低約250倍。

最後,研究人員解決了CNFET常見的功能問題。二進位計算需要兩種類型的電晶體:N型電晶體用 1 bit 打開,而 P 型電晶體則相反用 0 bit 關閉。一直以來,用碳奈米管製造這兩種類型的電晶體是一項挑戰,因為通常會產生性能各不相同的電晶體。為了解決該問題,研究人員開發出一種叫MIXED(metal interface engineering crossed with electrostatic doping,金屬介面工程與靜電摻雜交叉)的技術,它能精確地調整電晶體的功能和進行優化。

在這項技術中,他們把某些金屬(鉑或鈦)附著在每個電晶體上,這樣就可以將電晶體固定為 P 型或者 N 型。然後,他們通過原子層沉積將 CNFET 覆蓋到一種氧化的化合物上,從而使他們能夠調整電晶體的特性,以滿足針對不同應用程式而產生的特定要求。例如,伺服器通常需要運行速度快、耗電多的電晶體;而可穿戴裝置和醫療植入物可能需要運行較慢、功率較低的電晶體。

麻省理工學院的研究團隊表示,該製造技術現在已與一家矽晶片代工廠進行合作,推測應該是Analog Devices公司,預計在五年內可問世。因為,這項工作也得到了ADI公司,美國國家科學基金會和空軍研究實驗室的支持。(1505字;圖1)

參考資料:

MIT engineers build advanced microprocessor out of carbon nanotubes. MIT Technology Reviews, 2019/8/28.

Modern microprocessor built from complementary carbon nanotube transistors. Nature, vol. 572, pages595–602 (2019).

--------------------------------------------------------------------------------------------------------------------------------------------

【聲明】

1.科技產業資訊室刊載此文不代表同意其說法或描述,僅為提供更多訊息,也不構成任何投資建議。

2.著作權所有,非經本網站書面授權同意不得將本文以任何形式修改、複製、儲存、傳播或轉載,本中心保留一切法律追訴權利。

|